| isesimutil (r230) | 2012-01-01 23:07 |

| nbox_util (r247) | 2012-03-11 22:19 |

| noodlybox (0012) | 2010-01-01 19:46 |

| TimingChartViewer (r245) | 2012-02-15 00:10 |

図は作成中...

あなたを「CPUモデルを動かすために低レベルなソフトを書く」という作業から解放します。

図1

図1

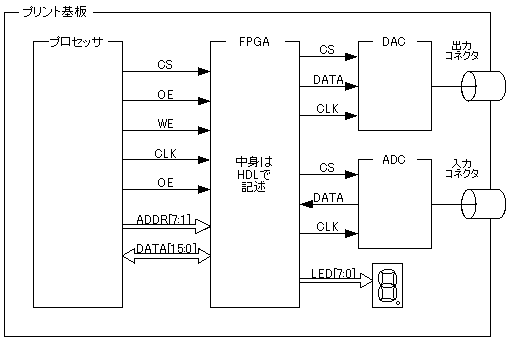

例えば図1のような製品を作るとします。プロセッサにとってDAC,ADC,LEDが単なるRAMに見えるように、図2のようにFPGAの中にレジスタを用意して、それを介してデータをやりとり可能にします。

FPGAのHDL記述を検証するためには、図3のように基板の上でFPGAと信号をやりとりしているLSIをHDLでモデル化し、シミュレータの上ですべてを動かせるようにする必要があります。

ここで、DAC, ADC, LEDは単純なのでモデル化にさほど苦労しませんが、プロセッサは複雑なのでモデル化は困難です。

また、プロセッサのモデルは扱う情報の量が多いため、必然的に図4のようなテキストファイルを$readmemh()で読み、解釈して、実行するという形になります。

問題は、

の2つです。

[PageInfo]

LastUpdate: 2010-02-13 17:00:11, ModifiedBy: molelord

[License]

![]() Creative Commons 2.1 Attribution

Creative Commons 2.1 Attribution

[Permissions]

view:all, edit:members, delete/config:members